| SPI | الجامعة السورية الخاصة<br>SYRIAN PRIVATE UNIVERSITY | كليية هندسة الحاسوب والمعلوماتية والاتصالات<br>Faculty of Computer & Informatics and<br>Communications Eng. |                 |                |                   |  |  |

|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------|--|--|

|     | الفترة الإمتحانية: الأولى                           | : الأحد 2019/01/06                                                                                          | اليوم و التاريخ | رات المنطقية   | اسم المقرر: الدار |  |  |

|     | مدة الامتحان: ساعة ونصف                             | الدرجة: خمسون                                                                                               | عدد الاسئلة: 7  | 5              | عدد الصفحات:      |  |  |

|     | الفصل: الأول                                        | العام الدراسي: 2018- 2019                                                                                   |                 | د.م. حسان أحمد | اسم المدرس:       |  |  |

|     |                                                     |                                                                                                             |                 |                |                   |  |  |

Part \_I. Choose the correct answer: [25 marks]

| 1.  | The number of values that can be assigned to a bit are                                         |   |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------|---|--|--|--|--|

|     | A. two B. ten C. eight D. one                                                                  |   |  |  |  |  |

| 2.  | AND, OR, and NOT gates can be used to form                                                     |   |  |  |  |  |

|     | A. storage devices B. all answers (A,C,D) C. comparators D. data selectors                     | • |  |  |  |  |

| 3.  | A shift register is an example of a                                                            |   |  |  |  |  |

|     | A. comparator B. counter C. storage device D. data selector                                    | • |  |  |  |  |

| 4.  | A device that is used to switch one of several input lines to a single output line is called a |   |  |  |  |  |

|     | A. comparator B. decoder C. demultiplexer D. multiplexer                                       |   |  |  |  |  |

| 5.  | The binary number 11011101 is equal to the decimal number                                      |   |  |  |  |  |

|     | A. 221 B. 121 C. 321 D. 212                                                                    | - |  |  |  |  |

| 6.  | The decimal number 250 is equivalent to the binary number                                      |   |  |  |  |  |

|     | A. 11110110 B. 11111010 C. 11111000 D. 11111011                                                | • |  |  |  |  |

| 7.  | The 2's complement of 11001100 is                                                              |   |  |  |  |  |

|     | A. 00110011 B. 00110101 C. 00110100 D. 00110110                                                | - |  |  |  |  |

| 8.  | The decimal number –234 is expressed in the 2's complement form as                             |   |  |  |  |  |

|     | A. 01011110 B. 10100010 C. 01011101 D. 11011110                                                |   |  |  |  |  |

| 9.  | An inverter performs an operation known as                                                     |   |  |  |  |  |

|     | A. both answers (B) and (C) B. complementation C. inversion D. all answers (A,B,C) are valid   |   |  |  |  |  |

| 10. | A Boolean expression that is in standard SOP form is                                           |   |  |  |  |  |

|     | A. the minimum logic B. has every variable C. contains only D. all answers                     |   |  |  |  |  |

|     | expression in the domain in one product term (A,B,C) are valid every term                      |   |  |  |  |  |

| 11. | Adjacent cells on a Karnaugh map differ from each other by                                     |   |  |  |  |  |

|     | A. two variables B. all variables C. one variable D. answer depends on the size of the map     |   |  |  |  |  |

| 12. | A variable is a symbol in Boolean algebra used to represent                                    | - |  |  |  |  |

|     | A. data B. a condition C. an action D. answers A, B, and C                                     |   |  |  |  |  |

| 13. | The Boolean expression $\overline{ABCD}$ is                                                    |   |  |  |  |  |

|     | A. a product term B. an inverse term C. a literal term D. all answers (A,B,C) are valid        |   |  |  |  |  |

| 14. | Which one of the following is not a valid rule of Boolean algebra?                             |   |  |  |  |  |

|     | A. $A + 1 = 1$ B. $A = \overline{A}$ C. $AA = A$ D. $A + 0 = A$                                |   |  |  |  |  |

| 15. | According to DeMorgan's theorems, the complement of a product of variables is equal to         |   |  |  |  |  |

|     | A. the complement of B. the product of the C. the sum of the D. answers A, B, and              |   |  |  |  |  |

|     | the sum complements complements C                                                              |   |  |  |  |  |

| 16.        | Decoder is a digital of                                                                   | circuit that converts           | coded info     | rmation in              | to a                  |                                            |   |

|------------|-------------------------------------------------------------------------------------------|---------------------------------|----------------|-------------------------|-----------------------|--------------------------------------------|---|

| 200        |                                                                                           | B. coded form                   | C. specifi     |                         |                       | swers (A,B,C) are not                      | t |

| 17.        | Encoder a digital circu                                                                   | it that converts info           | rmation to a   | coded form              |                       |                                            |   |

|            | A. noncoded form                                                                          | B. coded form                   | C. specifi     | ed form                 | D. all an<br>valid    | swers (A,B,C) are not                      | t |

| 18.        | <b>B.</b> Full-adder a digital circuit that adds two bits and an input carry to produce a |                                 |                |                         |                       |                                            |   |

|            | A. sum output only                                                                        | B. output carry on              | ly C. sun      | n and an out            | put carry             | D. all answers (A,B,C) are valid           | ) |

| 19.        | Multiplexer is a circu                                                                    | it that switches dig            | gital data fro | om several              | input lines           | onto a                                     |   |

|            | A. single output line                                                                     | B. multi single line            | output C       | 2. several<br>output li | single<br>ne          | D. all answers<br>(A,B,C) are valid        | 5 |

| 20.        | An active HIGH inpu                                                                       | it S-R latch is form            | ed by the c    | ross-coupli             | ing of                |                                            |   |

|            | A. two NAND gates                                                                         | B. two NOR g                    | gates C        | L. two OR               | gates                 | D. two AND gates                           |   |

| 21.        | A flip-flop changes i                                                                     |                                 |                |                         |                       |                                            |   |

|            | A. falling edge of th clock pulse                                                         | e B. rising edge<br>clock pulse |                | and (B)                 | swers (A)             | D. all answers<br>(A,B,C) are not<br>valid |   |

| 22.        | For an edge-triggered                                                                     | l D flip-flop,                  | i              |                         |                       |                                            |   |

|            | A. a change in the                                                                        | state B. the stat               | e that the     | C. the ou               | utput follov          | vs D. all answers                          | 3 |

|            | of the flip-flop can flip-flop goes to the input at each (A,B,C)                          |                                 |                | •                       |                       |                                            |   |

|            | occur only at a o                                                                         | -                               | s on the D     | clock                   | pulse                 | valid                                      |   |

| <u></u>    | pulse edge                                                                                | input                           |                |                         |                       |                                            |   |

| 23.        | J-K flip-flop is SET $-1$                                                                 |                                 |                |                         | _ 1                   | $\mathbf{D} \mathbf{I} = 1 \mathbf{V} = 0$ |   |

| 24.        | A. $J = 1, K = 1$<br>A register's function                                                | B. $J = 0, K = 0$               | <i>J</i>       | 2. $J = 0, K$           | - 1                   | D. $J = 1, K = 0$                          |   |

| <b>44.</b> | A legister s function<br>A. data storage                                                  | B. data moveme                  | nt C           | . neither (             | a) not $(\mathbf{b})$ | D. both (a) and (b)                        |   |

|            | Ų                                                                                         |                                 |                |                         | ······                |                                            |   |

| 25.        | To enter a byte of da                                                                     | ta serially into an 8           | -hit shift re  | gister ther             | e must be             |                                            |   |

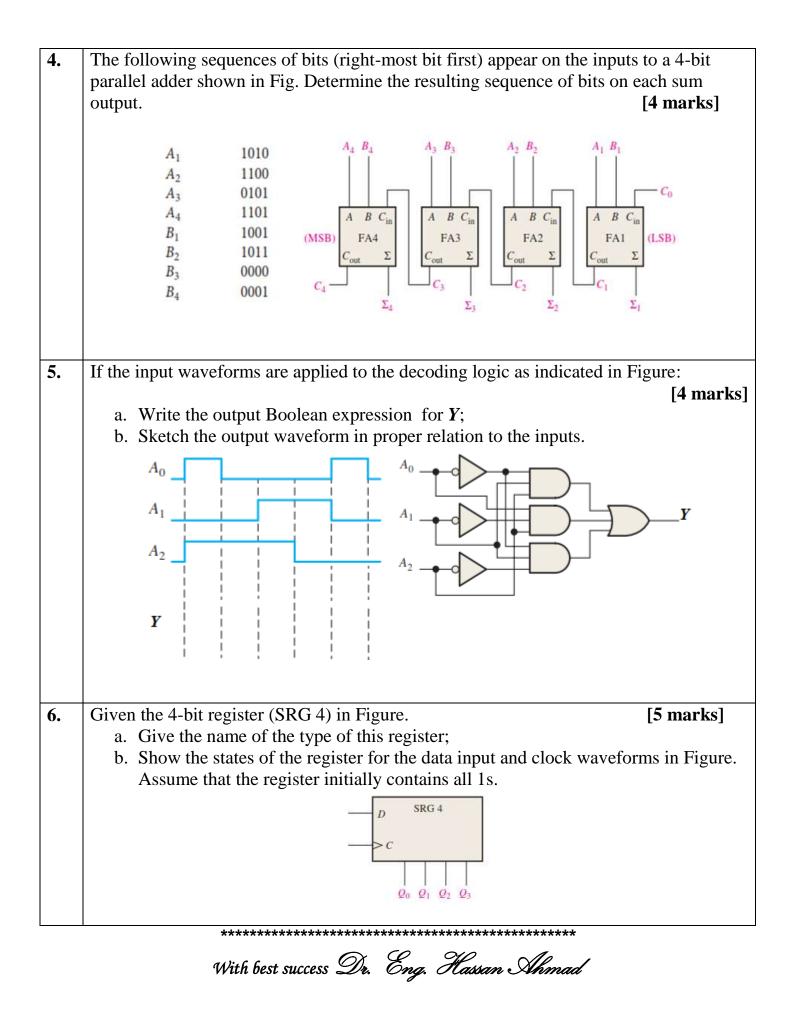

## Part II. Solve each of the following problems

| 1. | For the Exclusive-OR gate, write the Boolean expression and construct its truth table.                |

|----|-------------------------------------------------------------------------------------------------------|

|    | [4 marks]                                                                                             |

|    |                                                                                                       |

| 2. | Apply DeMorgan's theorems to each expression: [4 marks]                                               |

|    | a. $\overline{A(B+C)}$                                                                                |

|    | b. $\overline{(A+\overline{B})(\overline{C}+D)}$                                                      |

| 3. | Use a Karnaugh map to minimize the following standard SOP expression: [4 marks]                       |

|    | $\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$ |

|    |                                                                                                       |

|    |                                                                                                       |

|    |                                                                                                       |